1. Tujuan [back]

Data flip-flop merupakan dasar dari rangkaian utama sebuah memori penyimpan data digital.

2. Alat dan Bahan [back]

1. Gerbang NAND

menampilan nilai inverter dari input gerbang AND.jika output gerbang and berupa logika '1' maka pada gerbang nand outputnya akan menjadi logika '0'.

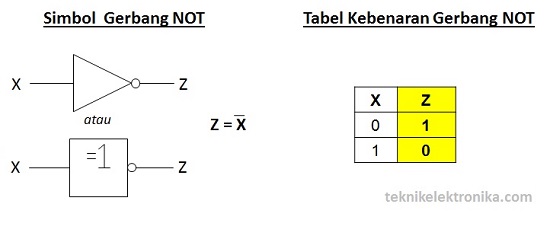

Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

3. Logicstate

untuk memberikan nilai logika 1 atau 0

4. Logicprobe

untuk menampilkan nilai keluaran, yang nilainya 0 atau 1.

3.Dasar Teori [back]

Data flip-flop merupakan pengemangan dari RS flip-flop, pada D flip-flop kondisi output terlarang (tidak tentu) tidak lagi terjadi. Data flip-flop sering juga disebut dengan istilah D-FF sehingga lebih mudah dalampenyebutannya. Data flip-flop merupakan dasar dari rangkaian utama sebuah memori penyimpan data digital. Input atau masukan pada RS flip-flop adalah 2 buah yaitu R (reset) dan S (set), kedua input tersebut dimodifikasi sehingga pada Data flip-flop menjadi 1 buah input saja yaitu input atau masukan D (data) saja. Model modifikasi RS flip-flopmenjadi D flip-flop adalah dengan penambahan gerbang NOT (Inverter) dari input S ke input R pada RS flip-flop seperti telihat pada gambar dasar D flip-flop berikut.

Gambar Rangkaian Dasar D Flip-Flop

Pada gambar diatas input Set (S) dihubungkan ke input Reset (R) pada RS flip-flop menggunakan sebuah inverter sehingga terbentuk input atau masukan baru yang diberi nama input Data (D). Dengan kondisi tersebut maka RS flip-flop berubah menjadi Data Flip-Flop (D-FF). Pada perkembanganya D flip flop ini ditambahkan dengan input atau masukan control berupa enable/clock seperti ditunjukan pada gambar berikut.

Gambar Data Flip-FLop Dengan Enable/Clock

Gambar diatas memperlihatkan Data flip-flop yang dilengkapi denganmasukan enable/clock. Fungsi input enable/clock diatas adalah untuk menahan data masukan pada jalur Data (input D) agar tidak diteruskan ke rangkaian RS flip-flop

contoh soal:

1.

Berikan argumen untuk membuktikan bahwa

output Q akan melacak input D hanya ketika input ENABLE tinggi.

2.

Buktikan bahwa output Q

memegang nilai itu sebelum input ENABLE pergi RENDAH selama input ENABLE adalah

RENDAH.

Solusi:

(1) Ketika input ENABLE adalah TINGGI,

gerbang AND bagian atas diaktifkan sementara gerbang AND bagian bawah dinonaktifkan.

Output dari gerbang AND atas dan bawah masing-masing adalah D dan logika ‘0’.

Mereka merupakan input dari gerbang NOR yang outputnya adalah D. Output Q

karena itu D.

(2.) Ketika input ENABLE menjadi RENDAH,

gerbang AND atas dinonaktifkan (dengan outputnya masuk ke logika '0') dan

gerbang AND lebih rendah diaktifkan (dengan outputnya menjadi sama dengan

Output Q karena umpan balik). Output gerbang NOR dalam kasus ini adalah Q, yang

berarti bahwa output Q tetap dalam statusnya selama input ENABLE adalah RENDAH.

1. Rangakaian 1 (gambar 10.40)

rangkaian diatas merupakan rankaian JK-flipflop sebagai D flip flop dan merupakan rangkaian dengan clock.

prinsip kerja dari rangkaian tersebut adalah saat logika input '1' maka rangkaian outputnya akan berupa logika '0' dan jika memiliki detak atau clock, output akan berubah-ubah dari '1' ke '0' secara bergantian tergantung detaknya. karena pada rangakaian d flip flop pada detakan pertama terdapat delay satu detakan maka output juga akan delay 1 detakan sehingga output pertamanya bernilai '0'.

2. Rangkaian 2 (gambar 10.42)

Saat rangkaian diberi logika '0' dab clock aktif, maka gerbang AND 1 akan beroutput '0', sedangkan gerbang AND 2 juga beroutput '0' karena salah satu kakinya berlogika '0'. selanjutnya, output dari kedua gerbang AND masuk ke gerbang NOR, sehingga output dari gerbang NOR adalah '1'. outout tadi di teruskan sebagai output komplimenter yang berlogika '1', dan output yang masuk ke inverter berupa output clock yang bergantian antara logika '1' dan '0'.

saat rangkaian diberi logika '1', gerbang AND 1 yang juga terhubung dengan clock akan menghasilkan output bergantian antara '1' dan '0', begitupun dengan gerbang AND 2, sehingga logika yang menjadi input pada gerbang NOR juga berganti-ganti, sehinga output yang dihasilkan berupa logika bergantian antara '1' dan '0', sehingga keluaran komplementernya berganti dari '1' ke '0', begitupun keluarannya.

saat diberi logika '0' dan clock aktif, keluaran dari D flip flop adalah '0' dan keluaran komplementernya '1'. sedangkan, saat diberi logika '1' keluaran akan menjadi '1' dan keluaran komplementer '0'. tetapi sebelum keluaran berganti satu terdapat delay satu detakan sebelum berubah, karena D flip flop bisa dikenal dengan delay flip flip yang menyebabkan nilai keluaran terhenti selama satu detakan.

2. Video Rangkaian 2 (gambar 10.42)

3. Video Rangkaian 3 (gambar 10.39)

Datasheet AND gate - download

Datasheet NAND gate - download

Datasheet NOT gate - download

Video Simulasi Rangkaian 1 - download

Video Simulasi Rangkaian 2 - download

Video Simulasi Rangkaian 3 - download

Simulasi Proteus Rangkaian 1 - download

Simulasi Proteus Rangkaian 2 - download

Simulasi Proteus Rangkaian 3 - download

File HTML - download

Tidak ada komentar:

Posting Komentar